异步FIFO结构框图解析

异步FIFO(First In First Out)结构框图解析:该结构主要由输入输出端口、写地址指针、读地址指针、存储单元和控制逻辑组成。当数据从输入端口进入FIFO时,写地址指针会移动,将数据存入存储单元;当数据从输出端口读出时,读地址指针会移动。由于异步设计,读写操作不受时钟同步限制,可实现不同速率的数据传输。该结构适用于高速、高效率的数据传输和处理。

在数字电路和通信系统中,异步FIFO(First In First Out,先进先出)结构是一种重要的数据缓冲机制,它广泛应用于高速数据传输、接口连接和存储系统中,以实现数据的异步传输和有效管理,本文将详细解析异步FIFO的结构框图及其工作原理。

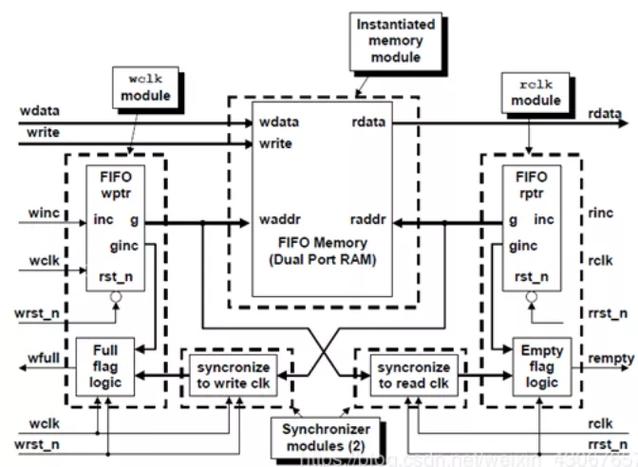

异步FIFO结构框图概述

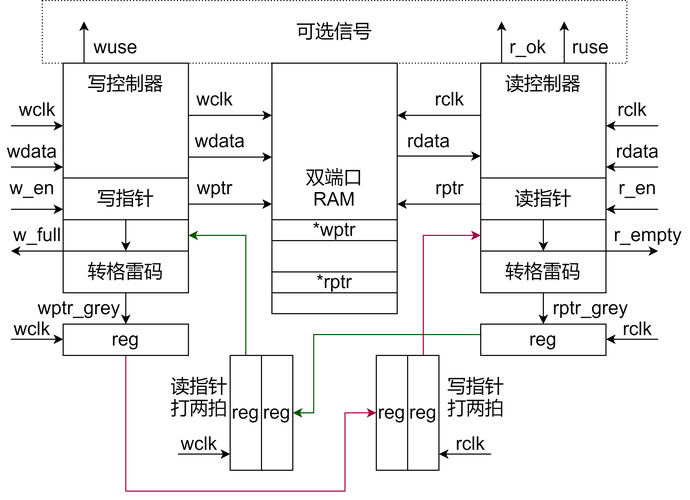

异步FIFO结构主要由以下几个部分组成:数据输入接口、数据输出接口、读写地址指针、存储单元和控制逻辑,这些部分相互协作,共同完成数据的异步传输和存储功能。

各部分详细解析

1、数据输入接口:数据输入接口是异步FIFO接收数据的端口,它接收来自外部系统的数据,并将其暂存于FIFO的存储单元中,数据输入接口通常包括数据输入线、时钟线、使能线等,以实现数据的同步输入。

2、数据输出接口:数据输出接口是异步FIFO输出数据的端口,它根据读写地址指针的指示,从存储单元中读取数据,并将其输出到外部系统,数据输出接口同样包括数据输出线、时钟线、使能线等,以实现数据的同步输出。

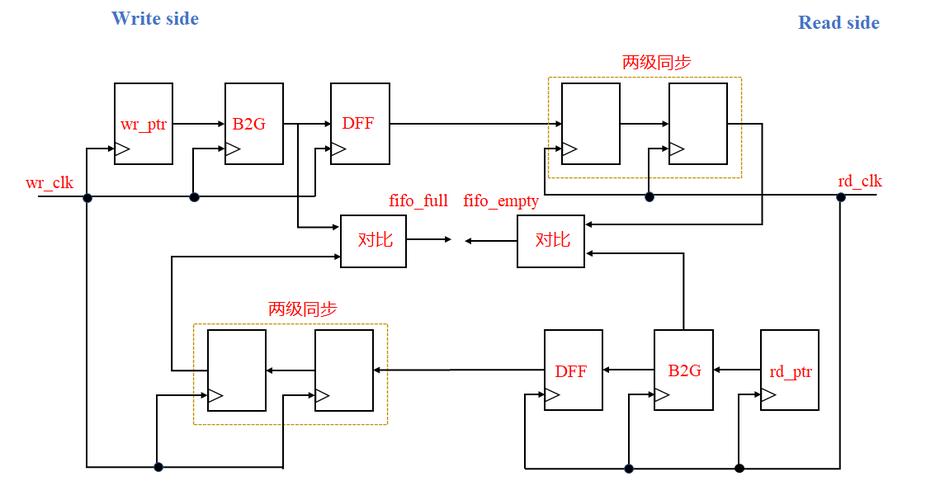

3、读写地址指针:读写地址指针是异步FIFO的核心部分之一,它负责跟踪存储单元中数据的读写位置,确保数据的先进先出特性,读写地址指针通常由控制逻辑驱动,根据读写操作的请求和状态,动态调整指针的位置。

4、存储单元:存储单元用于暂存数据的部分,它通常由一系列的寄存器或内存单元组成,具有较高的读写速度和较低的延迟,存储单元的大小根据应用需求而定,可灵活调整。

5、控制逻辑:控制逻辑是异步FIFO的另一核心部分,负责协调各部分的工作,它根据读写操作的请求、FIFO的状态以及外部系统的时钟信号,生成相应的控制信号,驱动读写地址指针和数据线的工作,控制逻辑还负责检测FIFO的空满状态,以防止数据溢出或读空等情况的发生。

工作原理

异步FIFO的工作原理可以概括为以下几点:

1、数据输入:当外部系统向数据输入接口发送数据时,控制逻辑根据读写地址指针的指示,将数据暂存于存储单元中。

2、数据读取:当外部系统发出读请求时,控制逻辑根据读写地址指针的位置,从存储单元中读取数据,并通过数据输出接口输出到外部系统。

3、空满检测:控制逻辑还负责检测FIFO的空满状态,当FIFO中的数据达到一定数量时,控制逻辑会发出相应的空满信号,以通知外部系统进行相应的操作。

4、异步传输:由于异步FIFO的读写操作是异步进行的,因此可以有效地避免因读写时钟不匹配而导致的性能瓶颈和数据丢失等问题。

异步FIFO结构框图是一种重要的数据缓冲机制,广泛应用于数字电路和通信系统中,它通过数据输入接口、数据输出接口、读写地址指针、存储单元和控制逻辑等部分的相互协作,实现了数据的异步传输和有效管理,异步FIFO具有较高的读写速度、较低的延迟和灵活的配置等特点,可满足不同应用的需求。