异步FIFO(First In First Out)实现原理详解

异步FIFO(First In First Out)实现原理详解:异步FIFO是一种用于不同时钟域之间数据传输的缓冲机制,其工作原理基于先进先出(FIFO)原则。通过读写指针的配合,异步FIFO能够确保数据的顺序性,并有效解决不同时钟域间数据传输的时序问题。其实现包括存储器、读写指针、状态机等部分,确保数据在传输过程中的准确性和可靠性。异步FIFO还具有空满标志位,以指示FIFO的状态,从而避免数据溢出或欠载等问题。

在数字电路和通信系统中,异步FIFO(First In First Out,先入先出)是一种重要的数据缓冲机制,它能够在不同时钟域之间进行数据传输,并有效地解决因时钟不同步而导致的读写冲突问题,本文将详细介绍异步FIFO的实现原理,包括其基本概念、设计思路、关键技术点及实际应用。

异步FIFO基本概念

异步FIFO是一种双端口RAM(Random Access Memory,随机存取存储器),具有两个独立的读写时钟域,它允许在不同的时钟频率下进行读写操作,从而解决因时钟不同步而导致的读写冲突问题,异步FIFO通常用于连接不同时钟域的设备,如FPGA(Field Programmable Gate Array,现场可编程门阵列)与外部存储器或处理器等。

异步FIFO实现原理

1、结构组成

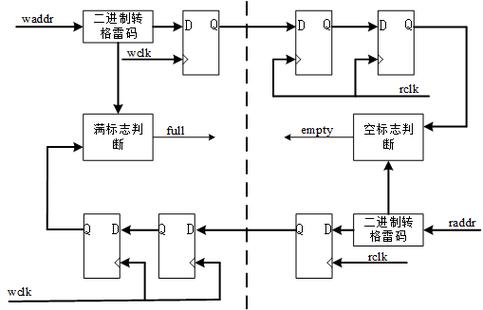

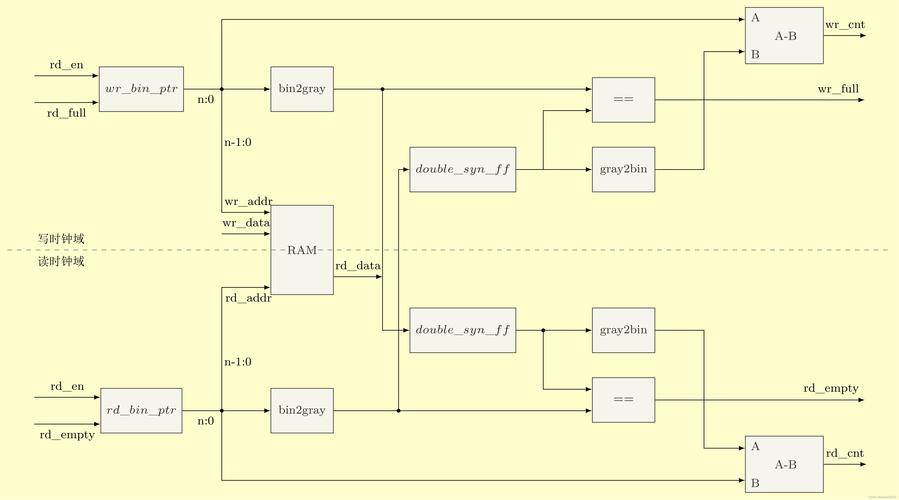

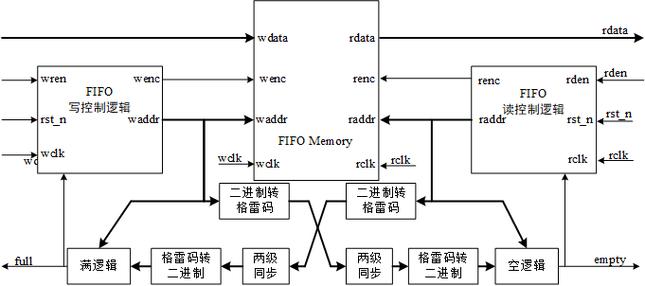

异步FIFO主要由读写地址生成器、数据存储器和状态控制逻辑三部分组成,数据存储器通常采用双端口RAM,以支持两个独立的读写时钟域。

2、读写地址生成器

读写地址生成器负责根据读写时钟和读写使能信号生成相应的读写地址,在异步FIFO中,读写地址生成器需要具备以下特点:

(1)支持不同时钟域下的读写操作;

(2)能够根据读写使能信号和当前状态生成正确的读写地址;

(3)具有防止读写冲突的机制,如写满判断、读空判断等。

3、数据存储器

数据存储器是异步FIFO的核心部分,用于存储待传输的数据,它通常采用双端口RAM,以支持两个独立的读写时钟域,在数据存储器中,每个存储单元都对应一个唯一的地址,读写操作通过地址访问相应的存储单元。

4、状态控制逻辑

状态控制逻辑负责监控异步FIFO的状态,如读空、写满等,并根据当前状态生成相应的控制信号,它通常包括以下部分:

(1)状态寄存器:用于存储异步FIFO的当前状态;

(2)状态判断逻辑:根据当前状态和读写使能信号判断异步FIFO的状态;

(3)控制信号生成器:根据状态判断结果生成相应的控制信号,如读写使能信号、空满标志等。

关键技术点

1、时钟域处理

异步FIFO需要在不同时钟域之间进行数据传输,因此需要处理时钟域的问题,常见的处理方法包括跨时钟域通信技术、时钟同步技术等,这些技术可以有效地解决因时钟不同步而导致的读写冲突问题。

2、空满判断及管理

为了防止异步FIFO的读空或写满导致数据丢失或错误,需要实现空满判断及管理机制,这通常通过比较读写地址、设置空满标志等方式实现,当异步FIFO的读空或写满时,需要停止相应的读写操作,并等待新的数据或空间可用后再继续操作。

3、同步与异步接口设计

异步FIFO的接口设计需要考虑同步与异步的问题,在接口设计中,需要明确区分同步和异步信号,并采用适当的接口协议进行通信,还需要考虑接口的可靠性和稳定性,以确保数据的正确传输。

实际应用及优化建议

异步FIFO广泛应用于数字电路和通信系统中,如FPGA与外部存储器或处理器的连接、高速数据传输等,在实际应用中,为了提高异步FIFO的性能和可靠性,可以采取以下优化建议:

1、优化读写地址生成器的设计,提高其响应速度和准确性;

2、采用高性能的数据存储器,如高速SRAM或DDR等;

3、优化状态控制逻辑的设计,使其能够快速准确地判断和处理各种状态;

4、采用适当的接口协议和通信技术,确保数据的正确传输和可靠性;

5、在实际使用中,还需要对异步FIFO进行严格的测试和验证,以确保其性能和可靠性满足要求。