异步FIFO设计的原理与实践

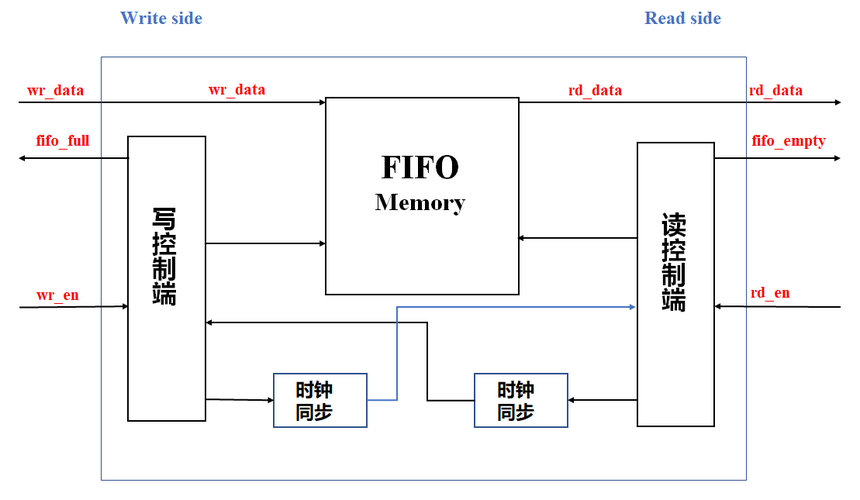

异步FIFO(First In First Out)设计原理与实践涉及电子工程与计算机科学领域。其原理基于先进先出的队列思想,用于不同时钟域间的数据传输,确保数据传输的准确性与高效性。实践中,异步FIFO设计需考虑读写时钟、空满标志、数据宽度等因素,通过状态机控制读写操作,实现数据的平滑流动。为防止数据溢出或欠读,需合理设置FIFO的深度与宽度。总体而言,异步FIFO设计是现代电子系统中的重要组成部分,其理论与实践的结合对于保障系统性能与稳定性具有重要意义。

在数字电路和通信系统中,异步FIFO(First In First Out,先进先出)设计是一种重要的存储和缓冲机制,异步FIFO设计能够有效地解决不同时钟域之间的数据传输问题,使得数据的读写操作在不同的时钟频率下能够顺利进行,本文将详细介绍异步FIFO设计的原理和实践应用。

异步FIFO设计的基本原理

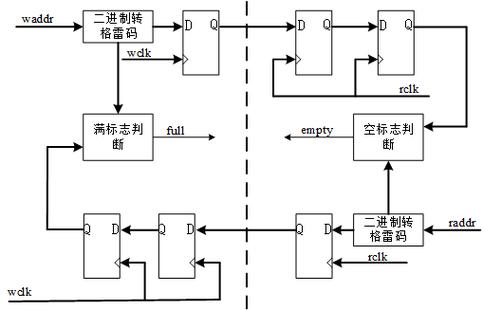

异步FIFO设计主要涉及到两个基本概念:读写指针和空满标志,读写指针用于跟踪FIFO中数据的读写位置,而空满标志则用于指示FIFO的空或满状态,异步FIFO设计的核心在于如何实现不同时钟域之间的读写操作同步。

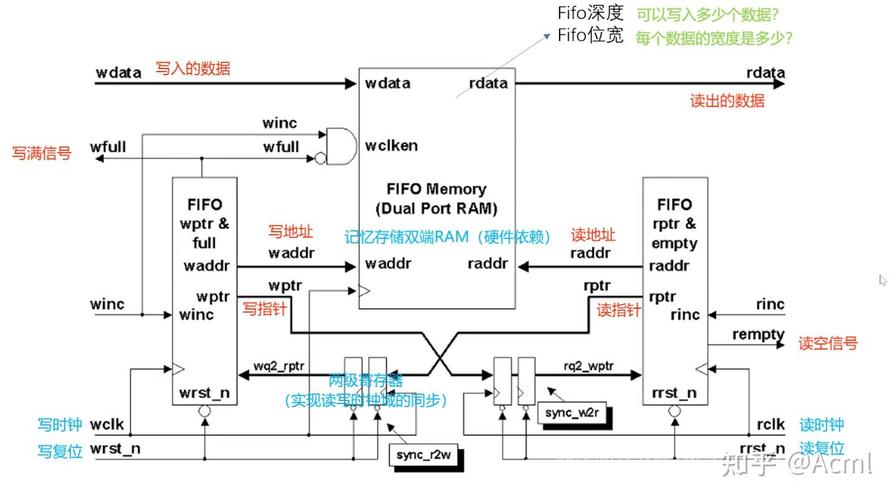

在异步FIFO设计中,通常采用双端口RAM作为存储介质,双端口RAM具有两个独立的读写端口,可以同时进行读写操作,通过控制读写指针的偏移量,可以实现数据的先进先出,为了实现不同时钟域之间的同步,还需要引入同步电路,如时钟域交叉(Clock Domain Crossing,CDC)技术。

异步FIFO设计的实现步骤

1、确定FIFO的深度和宽度,根据应用需求,确定FIFO能够存储的最大数据量和数据位宽。

2、选择合适的存储介质,在异步FIFO设计中,通常采用双端口RAM作为存储介质。

3、设计读写指针和空满标志,读写指针用于跟踪FIFO中数据的读写位置,而空满标志则用于指示FIFO的空或满状态,这些信号需要根据读写操作的状态进行更新。

4、实现不同时钟域之间的同步,通过引入同步电路,如CDC技术,实现不同时钟域之间的读写操作同步。

5、编写代码并进行仿真验证,根据设计要求,编写代码并使用仿真工具进行验证,在仿真过程中,需要关注读写操作的时序和数据的正确性。

异步FIFO设计的实践应用

异步FIFO设计在数字电路和通信系统中具有广泛的应用,在高速数据传输中,由于发送端和接收端的时钟频率可能不同,需要通过异步FIFO设计来缓冲和同步数据,在多核处理器、视频处理、音频处理等领域也需要使用异步FIFO设计来实现数据的存储和传输。

本文介绍了异步FIFO设计的原理和实践应用,异步FIFO设计能够有效地解决不同时钟域之间的数据传输问题,使得数据的读写操作在不同的时钟频率下能够顺利进行,通过双端口RAM和同步电路等技术的运用,可以实现高效的异步FIFO设计,未来随着技术的发展和应用场景的不断扩展,异步FIFO设计将有更广泛的应用前景。

异步FIFO设计是数字电路和通信系统中一种重要的存储和缓冲机制,通过深入理解其原理和实践应用,我们可以更好地应对不同场景下的数据传输问题,未来我们需要继续探索新的技术和方法,以实现更高效、更可靠的异步FIFO设计。