异步FIFO时序图详解

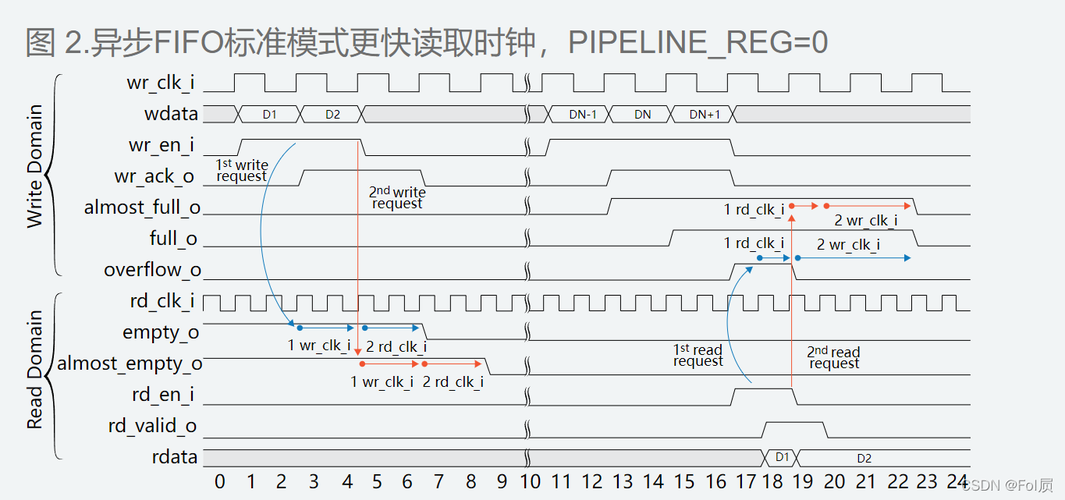

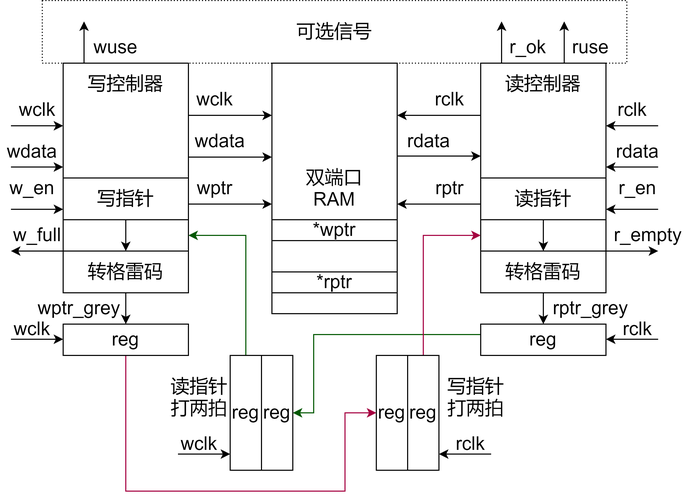

异步FIFO(First In First Out)时序图详解:该图展示了异步FIFO的读写操作、空满标志以及数据传输的时序关系。在读写过程中,通过控制读写使能信号和时钟信号,实现数据的异步读写。当FIFO满时,禁止写入操作,当FIFO空时,禁止读取操作,通过空满标志位进行控制。时序图中详细记录了读写操作的时序关系,以及数据在FIFO中的存取顺序,确保数据的正确性和高效性。

在数字电路和通信系统中,异步FIFO(First In First Out,先入先出)是一种重要的数据缓冲机制,它能够在不同的时钟域之间进行数据传输,并保证数据的正确性和时序性,异步FIFO的时序图是理解其工作原理和性能的关键,本文将详细介绍异步FIFO时序图的相关内容。

异步FIFO概述

异步FIFO是一种双端口RAM,其读写操作在不同的时钟域下进行,由于读写操作可能由不同的时钟信号控制,因此需要采用特殊的设计来保证数据的正确传输和同步,异步FIFO常用于高速数据传输系统中,如FPGA与SDRAM之间的数据交换、USB与主机控制器之间的数据传输等。

异步FIFO时序图

异步FIFO的时序图主要包括读写时钟信号、读写使能信号、数据输入/输出信号以及空满标志信号等,下面我们将详细介绍这些信号的时序关系。

1、读写时钟信号

异步FIFO的读写时钟信号可能来自不同的时钟域,读写时钟信号的频率和相位关系将直接影响FIFO的性能,在时序图中,读写时钟信号通常以周期性的方式出现,其周期与对应的时钟频率成反比。

2、读写使能信号

读写使能信号用于控制FIFO的读写操作,当读写使能信号有效时,相应的读写操作才能进行,在时序图中,读写使能信号的时序关系需要与读写时钟信号相配合,以保证数据的正确传输。

3、数据输入/输出信号

数据输入/输出信号是FIFO进行数据传输的媒介,在时序图中,数据的输入和输出需要在正确的时刻进行同步,以保证数据的正确性和时序性,当数据写入FIFO时,需要在写入时钟的有效期内将数据写入FIFO;当数据从FIFO中读出时,需要在读取时钟的有效期内从FIFO中读出数据。

4、空满标志信号

空满标志信号用于指示FIFO的状态,当FIFO中的数据量达到预设的阈值时,空满标志信号将发生变化,在时序图中,空满标志信号的变化需要与数据的读写操作相配合,以便系统能够及时地响应FIFO的状态变化。

异步FIFO时序图的解析

异步FIFO时序图的解析需要综合考虑以上各种信号的时序关系,下面我们将通过一个具体的例子来解析异步FIFO时序图。

假设有一个异步FIFO,其读写时钟分别为CLK_W和CLK_R,读写使能信号分别为WE和RE,数据输入/输出信号为DIN和DOUT,空满标志信号为EMPTY和FULL,在时序图中,我们可以看到以下几个关键点:

1、写入时钟的有效期:在每个CLK_W的上升沿,如果WE使能信号有效,则可以将DIN上的数据写入FIFO,这个时期称为写入时钟的有效期。

2、读取时钟的有效期:在每个CLK_R的上升沿,如果RE使能信号有效,则可以从FIFO中读出数据到DOUT,这个时期称为读取时钟的有效期。

3、空满标志的变化:当FIFO中的数据量达到预设的阈值时,EMPTY或FULL标志将发生变化,这个变化需要与数据的读写操作相配合,以便系统能够及时地响应FIFO的状态变化。

通过以上几个关键点的分析,我们可以更好地理解异步FIFO的时序图,并掌握其工作原理和性能。

异步FIFO的时序图是理解其工作原理和性能的关键,通过对异步FIFO时序图的详细介绍和解析,我们可以更好地掌握其读写操作的时序关系、空满标志的变化以及数据的正确传输,在实际应用中,我们需要根据具体的系统需求和性能要求来设计异步FIFO的参数和结构,以保证其能够满足系统的需求并发挥出最佳的性能。