异步FIFO设计要点详解

异步FIFO(First In First Out)设计要点详解:,,1. 接口设计:异步FIFO需考虑不同时钟域间的数据传输,确保读写时钟独立且互不干扰。,2. 空满标志:设计空满标志以指示FIFO的状态,避免读写冲突。,3. 深度与宽度:根据应用需求选择合适的FIFO深度和宽度,确保数据传输效率。,4. 同步与异步操作:需考虑读写操作的同步与异步问题,确保数据正确传输。,5. 防溢策略:设计防溢策略以防止FIFO溢出或欠读,保证数据完整性。,,以上是异步FIFO设计的关键要点,合理的设计能确保数据传输的稳定性和效率。

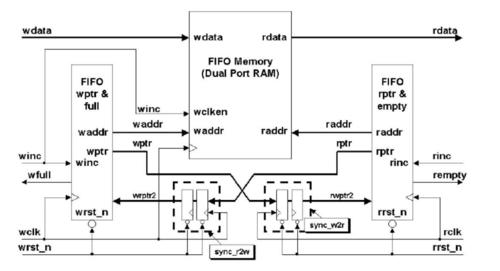

在数字电路设计中,异步FIFO(First In First Out,先进先出)是一种重要的数据缓冲结构,广泛应用于通信接口、数据传输和存储系统中,异步FIFO设计要点涉及到多个方面,包括接口协议、读写控制、空满标志设计等,本文将详细介绍异步FIFO设计的主要要点。

接口协议设计

异步FIFO的接口协议设计是整个设计的核心,由于读写操作可能来自不同的时钟域,因此需要设计一种能够跨时钟域通信的接口协议,这通常涉及到读写使能信号、数据输入/输出信号、空满标志信号等。

1、读写使能信号:读写使能信号用于控制FIFO的读写操作,当读写使能信号有效时,读写操作可以进行,为了防止数据在读写过程中发生冲突,需要确保读写使能信号的时序正确。

2、数据输入/输出信号:数据输入/输出信号用于在读写操作时传输数据,这些信号需要满足一定的时序要求,以确保数据的正确传输。

3、空满标志信号:空满标志信号用于指示FIFO的空或满状态,在异步FIFO设计中,空满标志的设计尤为重要,需要考虑到读写时钟域的差异,以及可能的亚稳态问题。

读写控制设计

读写控制是异步FIFO设计的关键部分,由于读写操作可能来自不同的时钟域,因此需要设计一种能够跨时钟域进行协调的读写控制机制。

1、读写时钟域分离:读写时钟域应相互独立,以避免时钟域之间的干扰,读写时钟的频率可以根据实际需求进行选择,以满足系统的性能要求。

2、读写使能同步化:为了确保读写的正确性,需要将读写使能信号进行同步化处理,这通常通过在读写使能信号的路径上添加适当的同步电路来实现。

3、读写指针管理:读写指针用于跟踪FIFO中数据的位置,在异步FIFO设计中,需要设计一种能够跨时钟域进行指针管理的机制,以确保读写的正确性和效率。

空满标志设计

空满标志是异步FIFO设计中的重要部分,用于指示FIFO的空或满状态,由于读写操作可能来自不同的时钟域,因此空满标志的设计需要考虑到时钟域的差异以及可能的亚稳态问题。

1、空标志设计:空标志用于指示FIFO中的数据为空,在异步FIFO设计中,空标志的设计应考虑到读写时钟域的差异,以及可能的亚稳态问题,通常采用双缓冲或双端口技术来实现空标志的准确判断。

2、满标志设计:满标志用于指示FIFO已满,以防止数据溢出,在异步FIFO设计中,满标志的设计同样需要考虑到时钟域的差异和亚稳态问题,通常采用一种特殊的计数器或比较器来实现满标志的判断。

3、亚稳态处理:由于异步FIFO设计中存在时钟域的差异,可能导致亚稳态问题的出现,为了解决这个问题,可以采取一些措施,如增加滤波电路、使用亚稳态避免技术等。

其他要点

除了以上几个要点外,异步FIFO设计还需要注意以下几点:

1、数据宽度和深度的选择:根据系统需求选择合适的数据宽度和深度,以满足数据的传输和处理要求。

2、功耗和性能的平衡:在满足系统性能要求的前提下,应尽量降低功耗,以提高系统的整体性能。

3、可靠性设计:考虑到系统可能面临的干扰和故障,应采取一些可靠性设计措施,如冗余设计、错误检测与纠正等。

异步FIFO设计要点涉及到接口协议、读写控制、空满标志设计等多个方面,在实际设计中,需要根据具体需求和约束进行综合考虑和权衡。